Chengjun Li

- Oct 21, 2014

- 84

- Joined

- Oct 21, 2014

- Messages

- 84

Hi everyone,

Please be patient allowing me to introduce the problem shortly.

I bought an evaluation board from a Japanese company recently. The board is used to measure very small capacitance difference by transfer input capacitance difference to output voltage, the resolution can reach 0.1fF. The board has three channels (X,Y,Z), and it can measure three capacitor pairs at the same time.

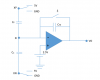

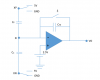

The working principle of the evaluation board is a Capacitance/Voltage conversion circuit shown below(X channel as an example).

SI terminal maintains at 2.5V. XP and XN are powered by square wave. Initially, XP is connected to 5V, XN is connected to GND, S is turned on, Cp and Cn are charged. Then, XP switched to GND, XN switched to 5V, at the same time, S is turned off. This way, the difference charges stored on Cp and Cn are transferred to CFB, the voltage across CFB is

V = (Cp – Cn) *5 / CFB

In the actual board, the circuit is added with a bootstrapping structure.

The board also has some internal registers which can adjust the gain, offset and compensate for temperature change.

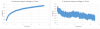

To test the board, I first connected the board to no external capacitor and measured the output voltage over a certain period of time( I only use X and Y channel). I found the output voltage is always stable over several hours.

Then, I connected the board to dummy capacitor pairs(capacitance of each capacitor is around 10pF).

The day I soldered the dummy capacitor on the board, the result I got is not stable.

I changed nothing and tested it again in the next day, the result became stable.

The third day the result is also stable.

Although I don’t know why the result in the first day is not stable, I think the board works fine based on the day 2 and day 3 results.

The next test I did is to connect the board to a DIP socket using copper wire, and placed the dummy capacitor on the socket(Capacitor only connected to X channel this time, Y channel connects nothing).

I placed the setup in an oven in order to have a stable environment and connected the oven to ground to make it serve like a faraday cage.

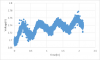

The results I got for three times test are very bad.

I don’t know what happened? I would be very grateful if anyone could give me some suggestion?

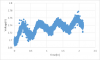

One thing I think I need to mention is the bad result seems have no laws, but sometimes I got the result with period. Like shown below.

Please be patient allowing me to introduce the problem shortly.

I bought an evaluation board from a Japanese company recently. The board is used to measure very small capacitance difference by transfer input capacitance difference to output voltage, the resolution can reach 0.1fF. The board has three channels (X,Y,Z), and it can measure three capacitor pairs at the same time.

The working principle of the evaluation board is a Capacitance/Voltage conversion circuit shown below(X channel as an example).

SI terminal maintains at 2.5V. XP and XN are powered by square wave. Initially, XP is connected to 5V, XN is connected to GND, S is turned on, Cp and Cn are charged. Then, XP switched to GND, XN switched to 5V, at the same time, S is turned off. This way, the difference charges stored on Cp and Cn are transferred to CFB, the voltage across CFB is

V = (Cp – Cn) *5 / CFB

In the actual board, the circuit is added with a bootstrapping structure.

The board also has some internal registers which can adjust the gain, offset and compensate for temperature change.

To test the board, I first connected the board to no external capacitor and measured the output voltage over a certain period of time( I only use X and Y channel). I found the output voltage is always stable over several hours.

Then, I connected the board to dummy capacitor pairs(capacitance of each capacitor is around 10pF).

The day I soldered the dummy capacitor on the board, the result I got is not stable.

I changed nothing and tested it again in the next day, the result became stable.

The third day the result is also stable.

Although I don’t know why the result in the first day is not stable, I think the board works fine based on the day 2 and day 3 results.

The next test I did is to connect the board to a DIP socket using copper wire, and placed the dummy capacitor on the socket(Capacitor only connected to X channel this time, Y channel connects nothing).

I placed the setup in an oven in order to have a stable environment and connected the oven to ground to make it serve like a faraday cage.

The results I got for three times test are very bad.

I don’t know what happened? I would be very grateful if anyone could give me some suggestion?

One thing I think I need to mention is the bad result seems have no laws, but sometimes I got the result with period. Like shown below.

Last edited: