I need to close the JFET in my sample and hold circuit with a postive voltage,

the reason being the sampling must be triggered by a keypress of my CV keyboard, so this mean using the 9V gate signal from the keyboard.

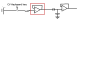

I made a schematic of an idea for this but im fairly sure it wont work,

however it does provide a good visual explantion of what im trying to do,

this will definitely hold the JFET open but I doubt connecting the gate to ground with the 3906 will close it.

there also would be resistors before the transistor base and gate, I just didnt bother adding them in.

:

the reason being the sampling must be triggered by a keypress of my CV keyboard, so this mean using the 9V gate signal from the keyboard.

I made a schematic of an idea for this but im fairly sure it wont work,

however it does provide a good visual explantion of what im trying to do,

this will definitely hold the JFET open but I doubt connecting the gate to ground with the 3906 will close it.

there also would be resistors before the transistor base and gate, I just didnt bother adding them in.

:

Last edited: